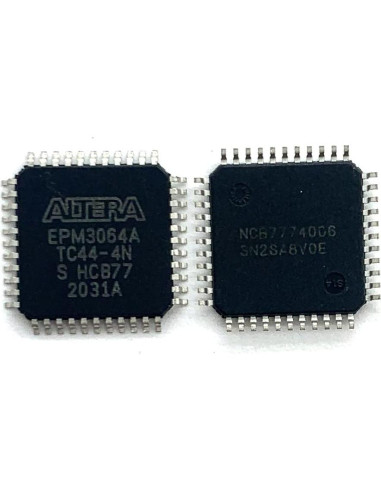

CARACTERÍSTICAS - Dispositivos lógicos programables (PLDs) basados en EEPROM CMOS de alto rendimiento y bajo costo construidos sobre una arquitectura MAX (ver Tabla 1) - Programabilidad en sistema de 3.3 V (ISP) a través de la interfaz JTAG del Grupo de Acción de Prueba Conjunta (IEEE Std. 1149.1) con capacidad avanzada de bloqueo de pines - Circuitería ISP conforme a IEEE Std. 1532 - Circuitería de prueba de escaneo de frontera (BST) incorporada conforme a IEEE Std. 1149.1-1990 - Características ISP mejoradas: - Algoritmo ISP mejorado para una programación más rápida - Bit ISP_Done para asegurar una programación completa - Resistor de pull-up en pines I/O durante la programación en sistema - PLDs de alta densidad que van de 600 a 10,000 puertas utilizables - Retrasos lógicos de pin a pin de 4.5 ns con frecuencias de contador de hasta 227.3 MHz - Interfaz I/O MultiVoltTM que permite que el núcleo del dispositivo funcione a 3.3 V, mientras que los pines I/O son compatibles con niveles lógicos de 5.0 V, 3.3 V y 2.5 V - Cantidades de pines que varían de 44 a 256 en una variedad de paquetes de tipo TQFP, PQFP, PLCC y FineLine BGA - Soporte para conexión en caliente - Estructura de enrutamiento continuo de matriz de interconexión programable (PIA) para un rendimiento rápido y predecible - Rango de temperatura industrial

Características destacadas

- - Dispositivos lógicos programables (PLDs) basados en EEPROM CMOS de alto rendimiento y bajo costo construidos sobre una arquitectura MAX (ver Tabla 1)

- - Programabilidad en sistema de 3.3 V (ISP) a través de la interfaz JTAG del Grupo de Acción de Prueba Conjunta (IEEE Std. 1149.1) con capacidad avanzada de bloqueo de pines - Circuitería ISP conforme a IEEE Std. 1532

- - Circuitería de prueba de escaneo de frontera (BST) incorporada conforme a IEEE Std. 1149.1-1990

- - Características ISP mejoradas: - Algoritmo ISP mejorado para una programación más rápida - Bit ISP_Done para asegurar una programación completa - Resistor de pull-up en pines I/O durante la programación en sistema

- - PLDs de alta densidad que van de 600 a 10,000 puertas utilizables

Especificaciones técnicas

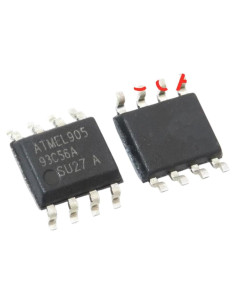

- Fabricante: XYwsh

- Peso: 0.2 kg

- Dimensiones: Ancho: 5.08 cm, Alto: 2.54 cm, Profundidad: 1.27 cm